This project focuses on designing and implementing a multi-cycle RISC-V processor using microprogrammed control. The processor is capable of executing R-type and I-type instructions, along with some other B_type like BNE and BGE.

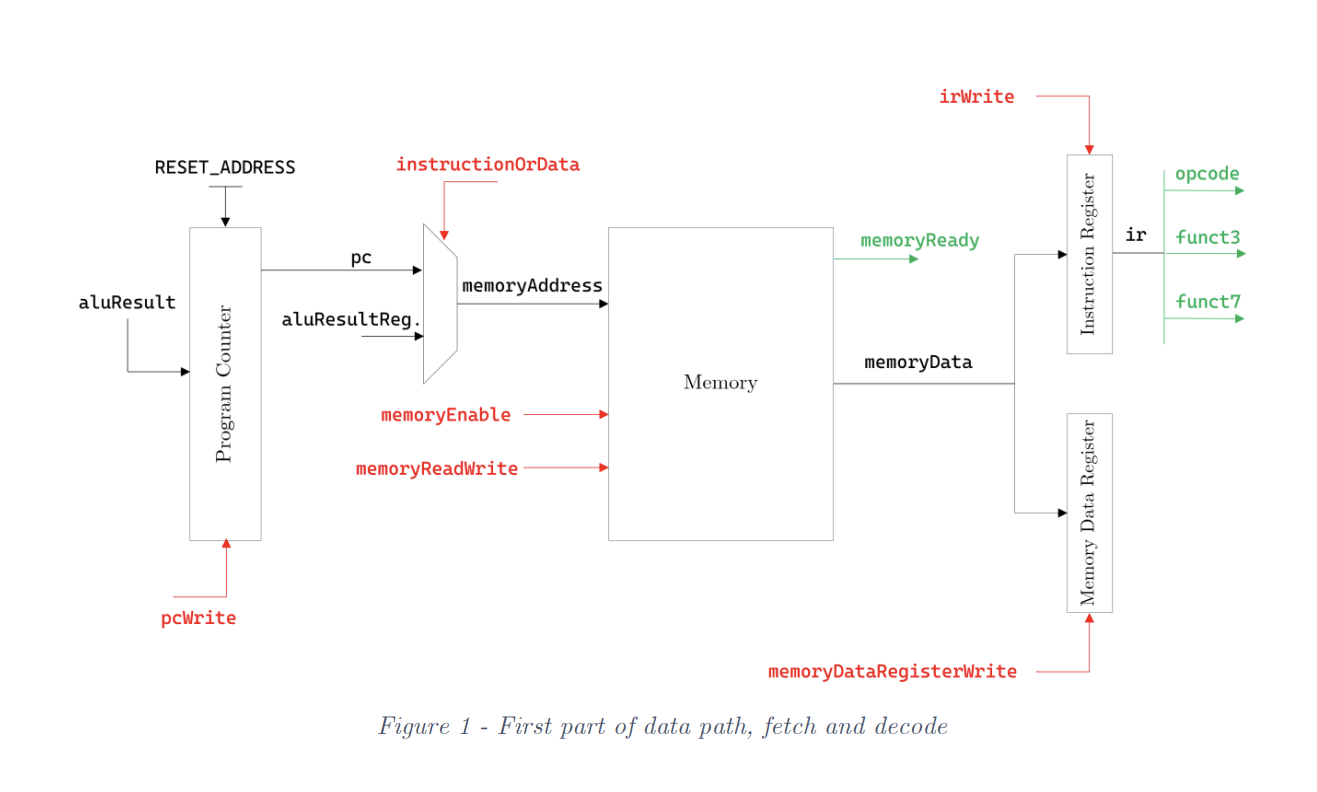

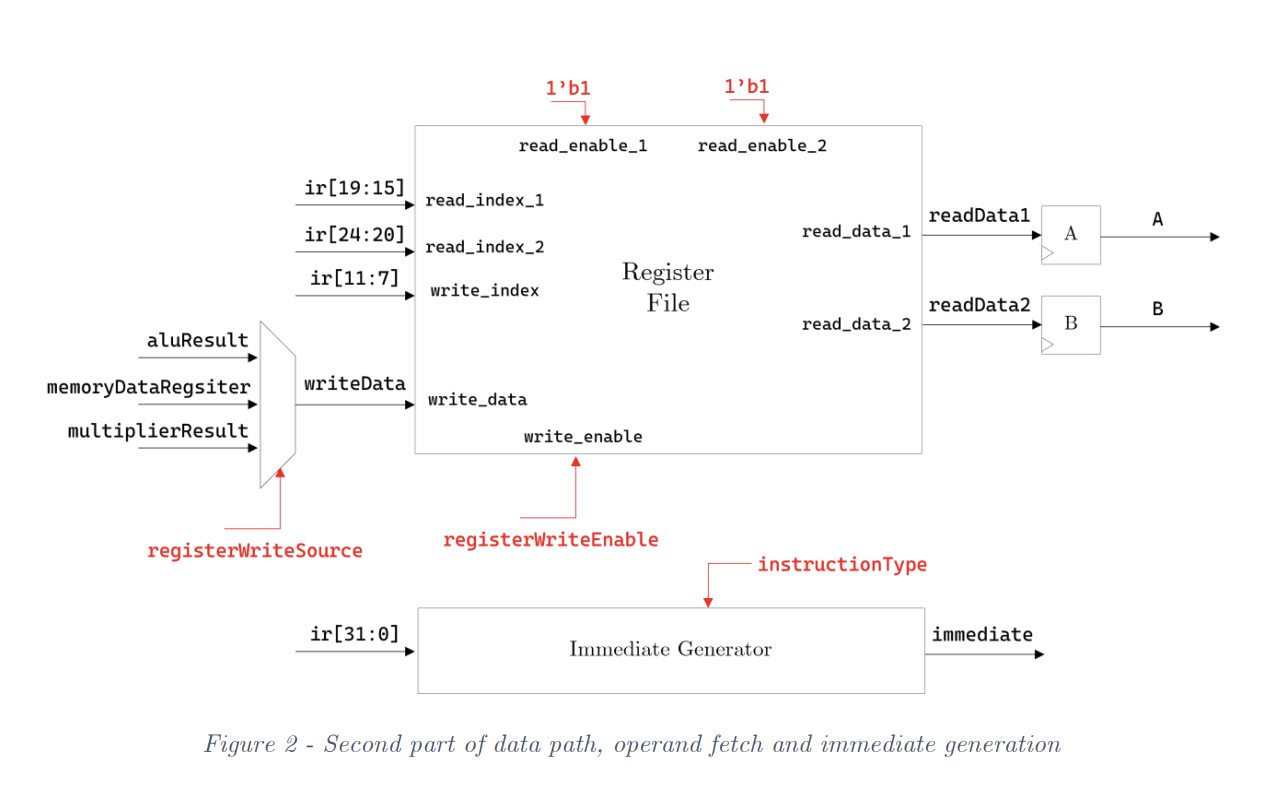

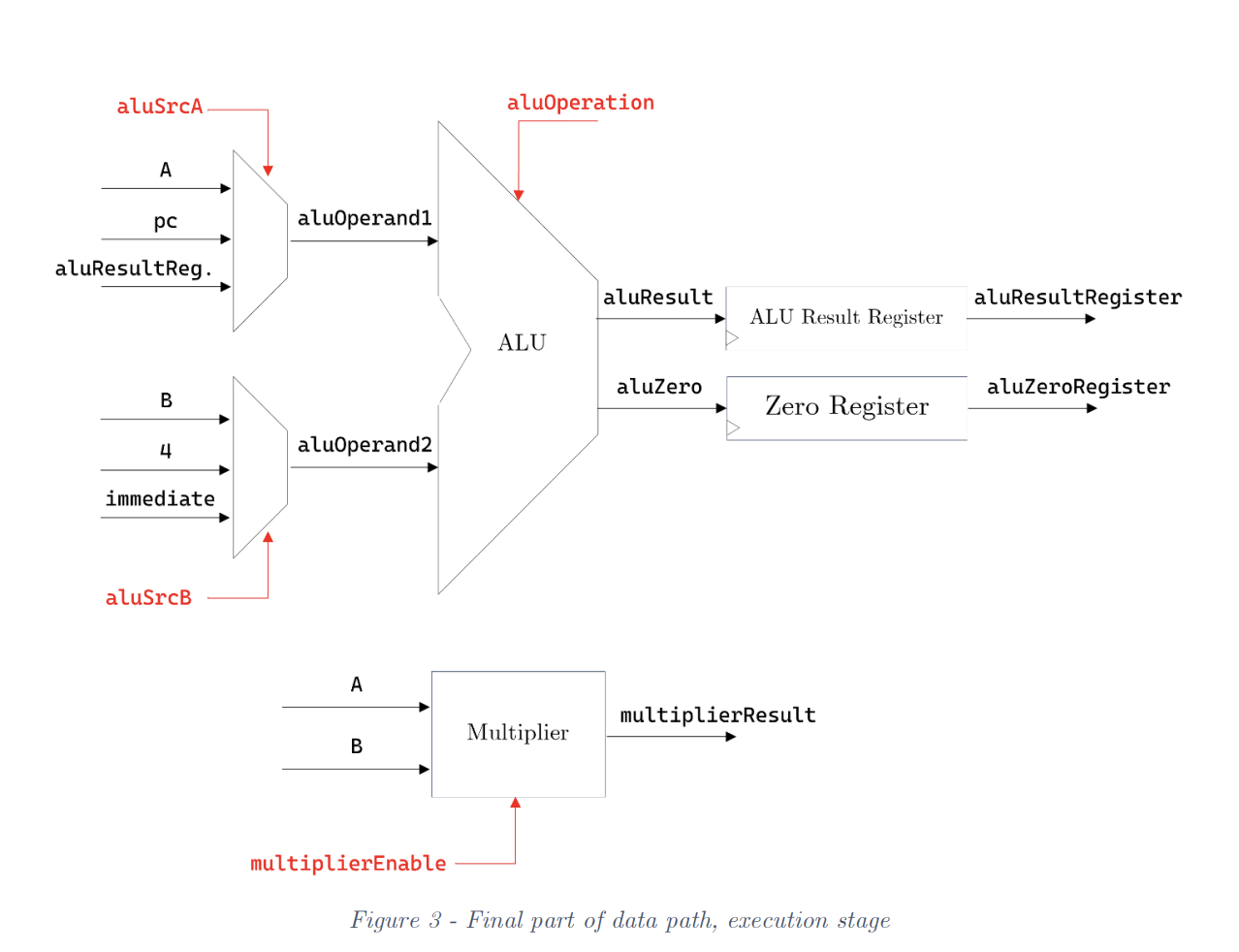

The processor consists of three main units: Memory, Data path and Controller.

In the multi-cycle design, a combined memory for instructions and data is used for more realistic and feasible operation. This enables reading the instruction in one cycle and reading or writing the data in another cycle. Data path design focuses on the design of ALU and other functional units as well as accessing the registers and memory. Control path design focuses on the design of the state machines to decode instructions and generate the sequence of control signals necessary to appropriately manipulate the data path.

Processsor Output: