-

Notifications

You must be signed in to change notification settings - Fork 8.2k

Boards: arm: gd32a503v_eval: introduce gd32a503v_eval board #52774

New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

Boards: arm: gd32a503v_eval: introduce gd32a503v_eval board #52774

Conversation

0e7f5eb to

6698d16

Compare

|

The following west manifest projects have been modified in this Pull Request:

Note: This message is automatically posted and updated by the Manifest GitHub Action. |

7a5f6b1 to

da51427

Compare

|

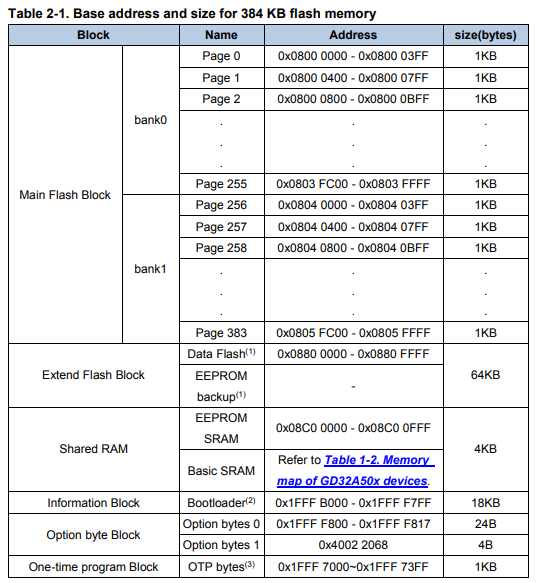

About FMC, I've checked #42809 , and I think |

Yes, it is. |

2062bbd to

4fd90e8

Compare

soc/arm/gigadevice/gd32a50x/soc.c

Outdated

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

Two things to take in consideration:

- Is it valuable check if

zephyr,sramwould be better option. - Is it possible to use memset ?

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

Is it valuable check if zephyr,sram would be better option.

fixed

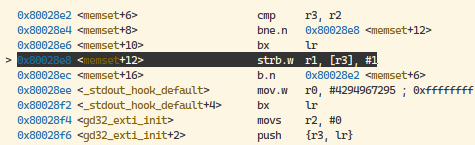

Is it possible to use memset ?

I’ve tried this, and got NMI exception at startup.

void z_arm_platform_init(void)

{

memset((void *)DT_REG_ADDR(DT_INST(0, SRAM)), 0, DT_REG_SIZE(DT_INST(0, SRAM)));

}I think the reason is memset store data by char, but memory want written in 32bit.

void *memset(void *buf, int c, size_t n)

{

unsigned char *d_byte = (unsigned char *)buf;

unsigned char c_byte = (unsigned char)c;

/* ...... */

while (n > 0) {

*(d_byte++) = c_byte;

n--;

}

return buf;

}4189506 to

15a87cc

Compare

15a87cc to

a63413c

Compare

|

Hi @feilongfl , In general you are doing a very good work. However, you need reorder you commits sequence as:

Why? If you look I'll wait you reorder the PR sequence to start review : ) |

40493d7 to

f5e4f7d

Compare

|

Hi @feilongfl , Please squash following commits:

|

f5e4f7d to

916262e

Compare

916262e to

143dcf1

Compare

3a0948d to

e7e213f

Compare

|

Hi @feilongfl , Please, rebase and fix conflict. After that update west.yml with new hash from hal. |

e7e213f to

846c3ae

Compare

add gd32a50x hal code Signed-off-by: YuLong Yao <[email protected]>

add gd32a50x series support Signed-off-by: YuLong Yao <[email protected]>

add support for gd32a50x Signed-off-by: YuLong Yao <[email protected]>

introduce gd32a50x series Signed-off-by: YuLong Yao <[email protected]>

soc: gd32a50x: introduce gd32a50x soc series Signed-off-by: YuLong Yao <[email protected]>

set port speed for `gd32a50x` Signed-off-by: YuLong Yao <[email protected]>

add gd32a50x support Signed-off-by: YuLong Yao <[email protected]>

add macro for gd32a50x Signed-off-by: YuLong Yao <[email protected]>

drop APB marco because clock_control driver is added. Signed-off-by: YuLong Yao <[email protected]>

add support for gd32a50x series. Signed-off-by: YuLong Yao <[email protected]>

introduce gd32a503v_eval board Signed-off-by: YuLong Yao <[email protected]>

add support for gd32a50x Signed-off-by: YuLong Yao <[email protected]>

add support for gd32a503v_eval board Signed-off-by: YuLong Yao <[email protected]>

add support for gd32a503v_eval board Signed-off-by: YuLong Yao <[email protected]>

add support for gd32a503v_eval board. Signed-off-by: YuLong Yao <[email protected]>

add unit test for gd32a503v_eval Signed-off-by: YuLong Yao <[email protected]>

846c3ae to

3792efa

Compare

cameled

left a comment

cameled

left a comment

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

LGTM, thanks @feilongfl !

nandojve

left a comment

nandojve

left a comment

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

Good work @feilongfl !

|

Note: this was merged adding binaries (cmsis-packs) to the module. I don't think this is acceptable, nor Zephyr's responsability, to host CMSIS packs. Please send a PR removing that from upstream Zephyr. |

| # SPDX-License-Identifier: Apache-2.0 | ||

| # | ||

|

|

||

| CONFIG_GPIO=y |

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

too late, but why doesn't board enable GPIO, as per-policy? this would not be needed at all.

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

Sorry, I didn't know about this policy before.

Are all boards supposed to have the following peripherals enabled by default?

CONFIG_CONSOLE=y

CONFIG_UART_CONSOLE=y

CONFIG_SERIAL=y

CONFIG_GPIO=y

Is there anything else I missed?

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

Yes, in general GPIO/UART are considered "minimal peripherals" used by lots of samples.

introduce gd32a503v_eval board

This is Gigadevice's first automotive chip with similar peripheral IP to STM32 or GD32.

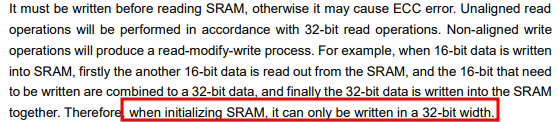

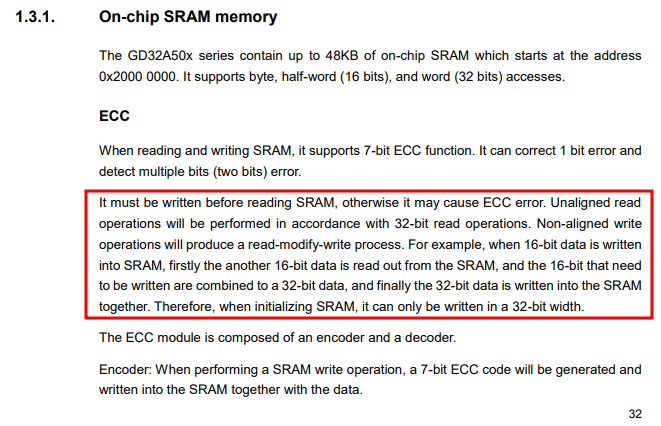

due to the following requirement of the ECC memory:

I enabled

CONFIG_PLATFORM_SPECIFIC_INITand implementz_arm_platform_initfunction insoc.cto clear all memory in da51427 . Without clear memory, it will fall into ecc nmi exception after power off reboot.I'm not sure if there is a better way to implement it.I split it from the soc implementation for review purposes.

todo:

About the IIC driver:

This SOC use a different IP, it changes a lot, so I decided not to implement it in this PR

other gigadevice works:

#38657